- 8 bit parallel in serial out shift register vhdl code full#

- 8 bit parallel in serial out shift register vhdl code code#

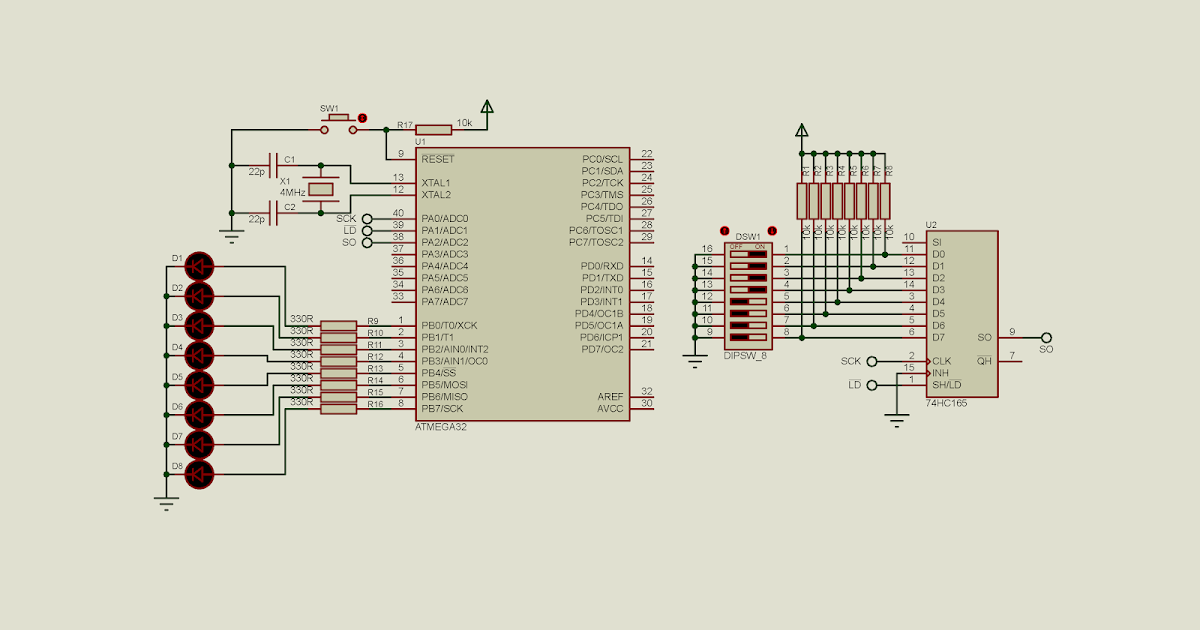

The VHDL allow assigning object of the same type in a single line of code.įor instance, you cannot perform the same assignment in C. In this description, the shift functionality is implemented using the assignment feature provided by VHDL. R_data <= i_data&r_data(0 to r_data'length-2) Type t_sreg is array(0 to 3) of std_logic_vector(1 downto 0) In the VHDL code, we used a type declaration for the shift register so the number of shift registers to be implemented can be passed as constant or generic in the VHDL entity. With respect to the shift register plainĭescription, the VHDL for-loop implementation can be parametrized.

8 bit parallel in serial out shift register vhdl code code#

Implementation, in terms of VHDL code description, can be achieved usingįor-loop iterative statement. For the variable the value is assigned immediately, it is not scheduled and it is performed immediately. In the case of shift-register implemented using variables, you must pay attention to the assignment order. It is a way to encapsulate the code, something like a component instantiation. So, you can use always the same process implementing a different set of shift-registers.

This approach is useful when you need different shift-register avoiding the declaration of a lot of signals.Īs you know, the variables are local to the process where you declare them.

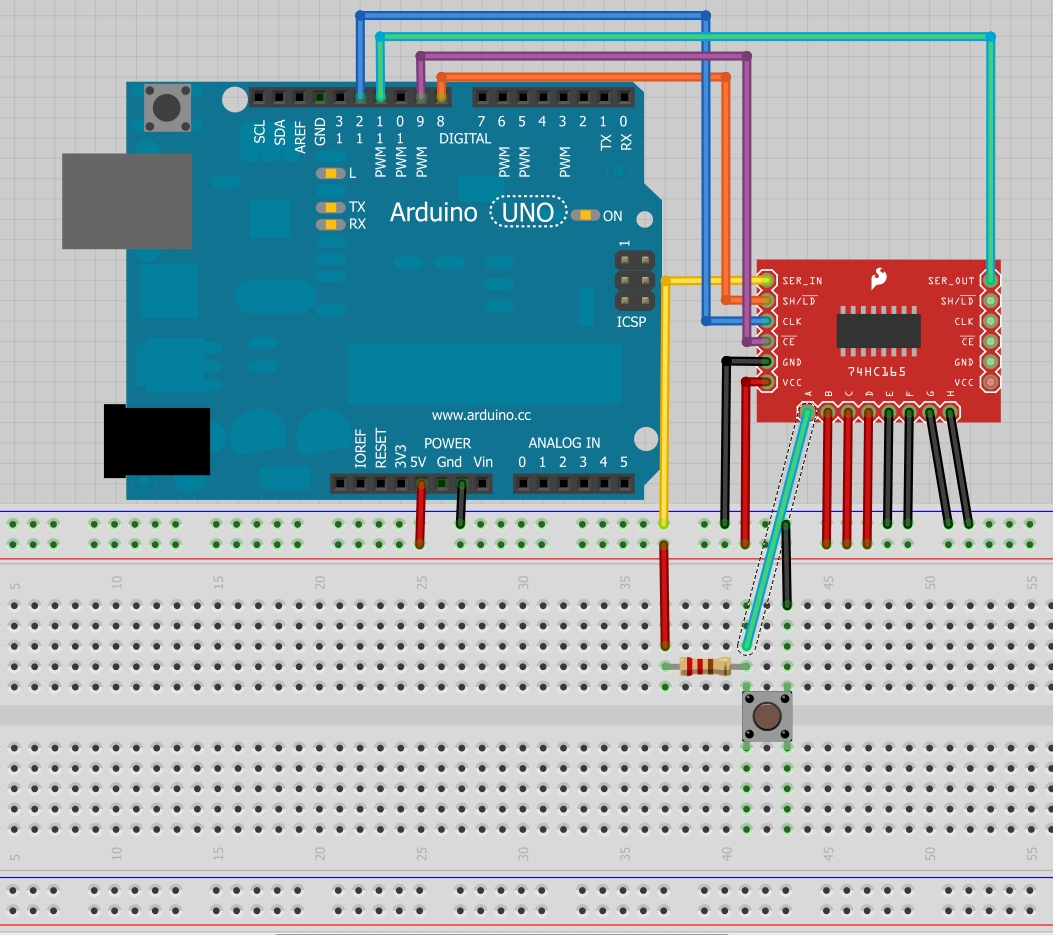

Set clock input C to 1MHz, serial input DATA to 1010, and reset signal à to 0 initially (up to 2us) and 1 after 2us (3) Explain, in detail, how you would modify your VHDL code in Question 2 to add shifting direction control input (DIR).

8 bit parallel in serial out shift register vhdl code full#

Do not crop your screen capture, it should show your full PC screen. Note 2: Include screenshots for the VHDL code and simulation result. Note 1: 'Set End Time' to 8us, and 'Grid Size' to lus. Include the screenshot of VHDL code and screenshot of simulation result. Set clock input C to 1MHz, serial input signal DATA to 1010, and reset signal R to 0 initially (up to 2us) and 1 after 2us and perform functional simulation of your circuit. Shifting direction is "right-to-left" (from LSB (20) to MSB (07), and QO is set to the value of serial DATA input bit on a positive edge of clock signal). Transcribed image text: (2) Write VHDL code to implement a positive edge-triggered 8-bit Serial In/Parallel Out (SIPO) shift register with asynchronous active- low register Reset input (Ⓡ).

0 kommentar(er)

0 kommentar(er)